Tetstbench까지 만들었으면 simulation을 진행 할 수 있다.

iverilog가 설치 되어 있으면 아래와 같은 명령으로 simulation을 수행한다.

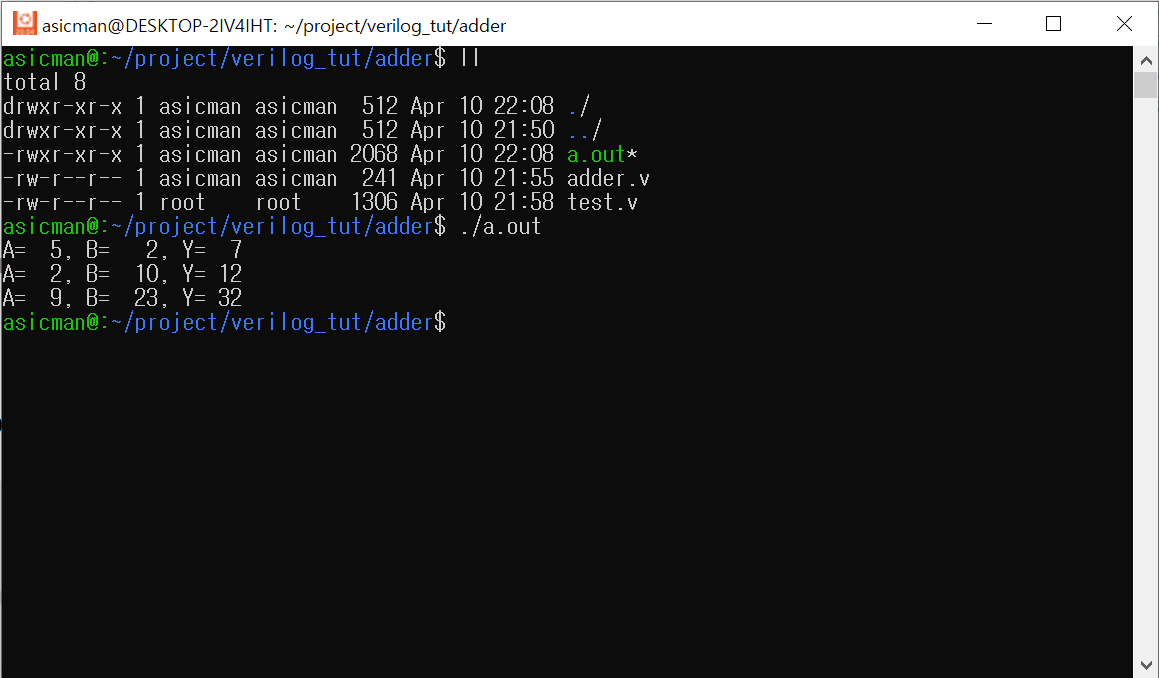

>>iverilog adder.v test.v위의 명령을 실행하고 디렉토리 리스트를 보면 a.out 라는 실행 파일이 생성된 것을 볼 수 있다.

이를 실행 시키면 아래 그림 처럼 a,b,y에 대한 값이 정상적으로 출력 되는 것을 볼 수 있다.

iverilog 실행 시 출력으로 생성되는 실행 파일의 이름을 지정할 수 있는데 아래와 같이 하면 된다.

iverilog -o test_adder adder.v test.v이렇게 하면 a.out이 아니라 test_adder라는 이름의 실행 파일이 생성되고 마찬가지로 이를 실행 시키면 simulation이 수행된다.

이렇게 $display 문을 이용하여 simulation결과를 확인할 수도 있지만 각 신호의 파형을 확인해 보고 싶을 수가 있다. 이럴 때는 $dumpfile과 $dumpvars로 시작하는 waveform dump 명령을 테스트벤치 상에서 사용할 수 있다. 아래는 test module아래의 모든 변수를 dump하는 예이다. 별도의 initial문을 이용하여 dump file을 지정하고 dump할 변수를 지정하였다.

initial

begin

$dumpfile("test_adder.vcd");

$dumpvars(0, test);

end$dumpvars의 사용법은 다음과 같다. 첫 번재 파라메터는 dump level을 지정한다.

| dump level | 변수 범위 |

| 0 | 지정한 module 에 포함된 모든 module의 변수 |

| 1 | 지정한 module의 변수 |

| 2 | 지정한 module과 하나 아래 단계의 module의 변수 |

두번 째 파라메터는 특정 module이나 변수를 지정한다. 위 예제에서는 testbench module인 test를 지정하였다.

이렇게 하여 simulation을 수행하면 test_adder.vcd file이 생성되고 아래와 같이 waveform을 열어서 확인할 수 있다.

>>gtkwave test_adder.vcd

위 그림에서 adder 모듈의 instance인 u_adder를 클릭하면 해당 module에 선언된 변수들을 확인할 수 있다.

'실전! Verilog HDL RTL Design' 카테고리의 다른 글

| [Verilog HDL] 8. 순차논리 (Sequential Logic) Adder 설계 (0) | 2022.05.04 |

|---|---|

| [Verilog HDL] 7. 순차논리 (Sequential Logic) 회로 설계 (D F/F) (0) | 2022.04.10 |

| [Verilog HDL] 5. Testbench (0) | 2022.03.28 |

| [Verilog HDL] 4. Adder 설계 (0) | 2022.03.25 |

| [Verilog HDL] 3. Combinational Logic/Sequential Logic (0) | 2022.03.25 |