APB는 주로 peripheral device같은 작은 디바이스를 버스에 연결하기 위하여 사용되는 AMBA bus 표준의 하나이다. Protocol이 간단하기 때문에 구현하는 로직도 작아 파워도 적게 소모되는 장점이 있다. 하지만 고속 데이터 전송에는 적합하지 않기 때문에 주로 hardware IP의 레지스터를 읽고 쓰는데 사용되는 protocol이다.

APB protocol spec은 아래 링크에서 받아 볼 수 있다.

https://web.eecs.umich.edu/~prabal/teaching/eecs373-f12/readings/ARM_AMBA3_APB.pdf

앞서 설계한 레지스터 파일은 IP 안에 포함되게 되는데 이를 버스에 연결하려면 APB interface를 구현해야 한다.

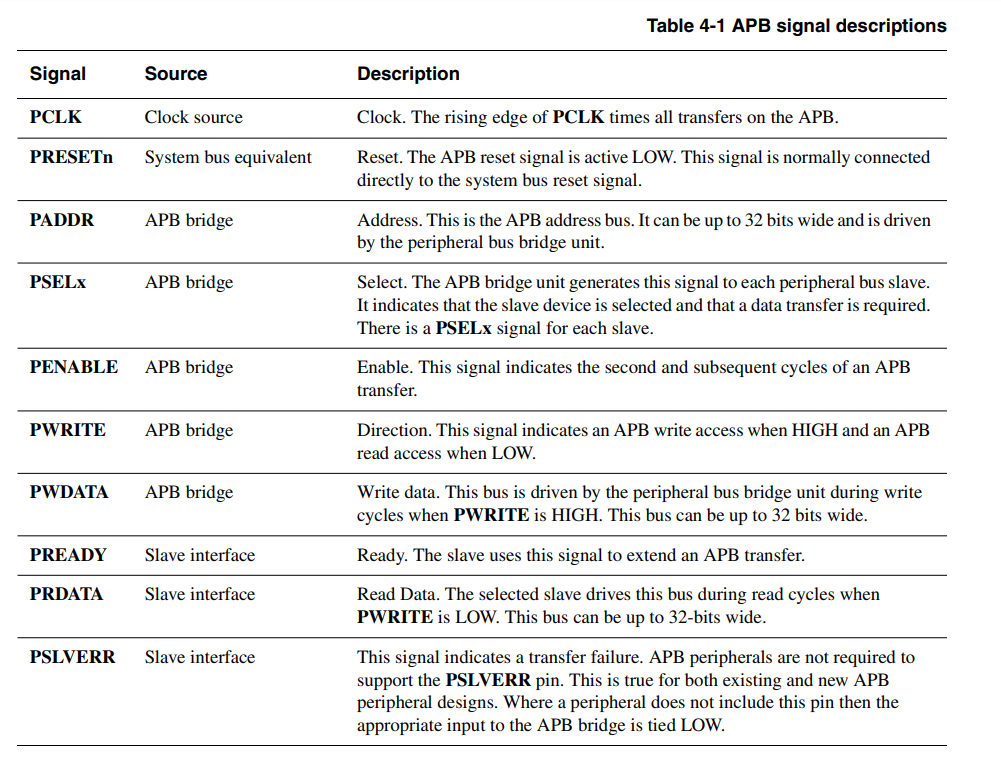

APB interface에 필요한 pin은 위의 spec에 나와 있는데 아래와 같다.(spec 42page)

결국은 레지스터 파일에 read/write 동작을 수행해야 하므로 spec에서 중요한 부분은 read/write timing diagram이다.

먼저 read timing diagram은 아래와 같다. (spec 23page)

위의 그림은 wate 상태가 포함된 그림인데 wait상태란 PREADY가 '0'일 경우를 말한다.

구체적으로 설명하면, 초기 상태는 PSEL과 PENABLE이 모두 '0'인 상태로 IDLE state라고 한다. PCLK의 positive edge에서 PWRITE를 '0'으로 만들고, PSEL을 '1'로 만든다. 이를 SETUP state라고 하는데 이는 PSEL에 연결되어 있는 Peripheral IP에 읽기 동작을 수행하겠다는 의미이다(T1 cycle). T2 cycle에서 PENABLE을 '1'로 만들어 IP에서 data를 출력해야 함을 알려 준다. 이를 ACCESS state라고 한다. T3에서 PREADY가 '1'이면 IP에서 데이터를 출력했으므로 읽어가도 된다는 의미이고 PREADY가 '0'이면 아직 데이터가 준비되지 않았으므로 PREADY가 '1'이 될 때까지 기다려야 한다는 의미이다. T3에서 PREADY가 '0'이므로 한 클록 기다리고 T4에서 마찬가지로 PREADY를 검출한다. 이 때도 '0'이므로 한 클록 더 기다리고 T5에서 PREADY가 '1'이므로 PRDATA에 실린 데이터를 읽어 오면서 PSEL과 PENABLE을 '0'으로 만들어 다시 SETUP state로 돌아가게 한다. 주의할 점은 PREADY가 '0'인 구간에서는 PADDR, PWRITE, PSEL, PENABLE을 이전 값으로 항상 유지하고 있어야 한다는 것이다.

write 동작의 timing diagram은 아래와 같다.

IDLE상태에서 SETUP상태, 그리고 ACCESS 상태로 전이하는 것은 read와 동일하다 단 PWRITE신호가 '1'이 되어 write transfer임을 나타낸다. 결과적으로 T5시간의 PCLK positive edge에서 Data 1이 Addr 1에 써지게 된다.

이러한 상태 변화를 그림으로 나타낸 것을 state diagram이라고 한다. 아래는 APB protocol에 대한 state diagram을 보여준다.

디저털 회로에서 이러한 state 전이를 구현하여 제어 로직을 만들 수 있는데 이러한 HW를 Finite State Machine 줄여서 FSM이라고 한다. FSM에서는 state와 입력 신호를 가지고 필요한 제어 로직을 만든다. 결국 APB interface를 이용한 register file을 만드는데 FSM을 이용하면 되는 것이다. 그러면 다음 장에서 FSM을 이용하여 APB interface를 가지는 register file을 verilog로 설계하도록 하겠다.

'실전! Verilog HDL RTL Design' 카테고리의 다른 글

| [Verilog HDL] 16. FSM을 이용한 APB register file 설계 (0) | 2023.01.27 |

|---|---|

| [Verilog HDL] 15. regfile.v를 최적화 하자.(parameter와 배열 인덱싱 기법) (0) | 2022.12.26 |

| [Verilog HDL] 13. Register File (0) | 2022.09.14 |

| [Verilog HDL] 12. IP, Bus, SoC (0) | 2022.08.01 |

| [Verilog HDL] 11. ALU (Arithmetic Logic Unit) 설계 (2) | 2022.06.03 |